电磁干扰(EMI)历来是让PCB设计工程师们头疼的一个问题,它威胁着电子设备的安全性、可靠性和稳定性。因此,我们在设计PCB时,需要遵循一定的原则,使电路板的电磁干扰控制在一定的范围内,达到设计要求和标准,提高电路的整体性能。

电磁干扰有传导干扰和辐射干扰两种。传导干扰是指通过导电介质把一个电网络上的信号耦合(干扰)到另一个电网络。辐射干扰是指干扰源通过空间把其信号耦合(干扰)到另一个电网络。在高速PCB及系统设计中,高频信号线、集成电路的引脚、各类接插件等都可能成为具有天线特性的辐射干扰源,能****电磁波并影响其他系统或本系统内其他子系统的正常工作。

我们是否因为 EMI 问题而避免使用多通道继电器驱动器?这个 EMI 问题可以通过增加上升/下降时间来解决,这样到负载的电路板走线就不会像传输线一样起作用。降低输出压摆率将增加上升和下降时间。可以通过添加电阻器 (Rin) 和电容器 (Cint) 来控制驱动器压摆率,从而形成积分器。砰!问题解决了......这是如何做到这一点以及我们会发现的典型结果:

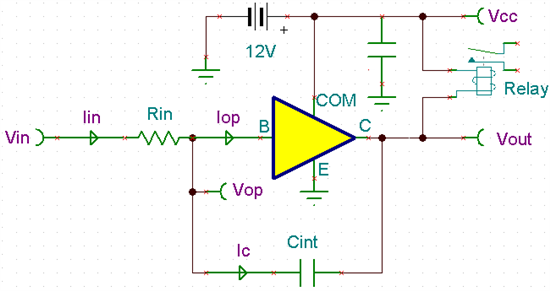

图 1:示意图

第 1 步:根据驱动器的工作点估算电容电流

驱动器输入电压 (Vop) 和输入电流 (Iop) 在输出压摆时间内几乎保持不变。对于输入电阻 (Rin) 的实际值,驱动器输入电流 (Iop) 将远小于电阻电流 (Iin)。因此,电容器电流 (Ic) 可以近似为与输入电流相同。

对于EMI传导部分,重点是充分利用旁路电容器和去耦电容器。旁路电容器(提供交流短路线)必须布置在晶片电源管脚和接地线(平面)上。去耦电容器应放置在电流需求变化较大的地方,以避免因电线阻抗(电感)而从电源和接地线上耦合干扰。当然,磁珠的合理串联可以吸收(转换为热能)。电感器有时也可以用来过滤干扰,但请注意,电感本身也有频率响应范围,包装也决定了其频率响应。以上是一些基本的经验,对于EMI设计,你需要真正了解自己的设计,需要关注哪里,问题会是什么现象,什么是替代方案,需要提前整理。

第 2 步:确定正压摆率和负压摆率

正输出压摆率(输入逻辑低电平)为 (Vop - Vin) / (Rin * Cint),单位为 V/S。负输出压摆率(输入逻辑高电平)为 (Vin - Vop) / (Rin * Cint),单位为 V/S。除以 10 6得到 V/uS 。Iop 和 Vop 随负载和温度而变化。它们还可以因设备而异。由于这些差异,速率控制很好,但精度不高。

对于我们的实验,我们使用 Rin=402 ohms,继电器为 12V,线圈电流为 122mA,Vop = 1.7V,Iop = 90uA,Cint = [0.1nF,1nF,10nF,100nF],VIH = 3.2V,VIL=0.1V ,结果如下:

腰带积极的消极的

nF转换速率转换速率单位

没有任何170900V/uS

0.125.933.4V/uS

13.823.71V/uS

100.3760.379V/uS

1000.0310.030V/uS

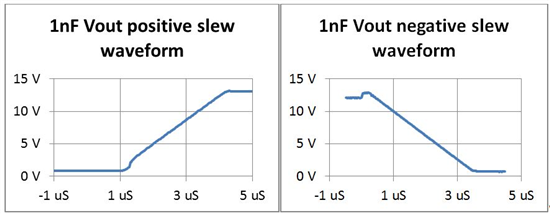

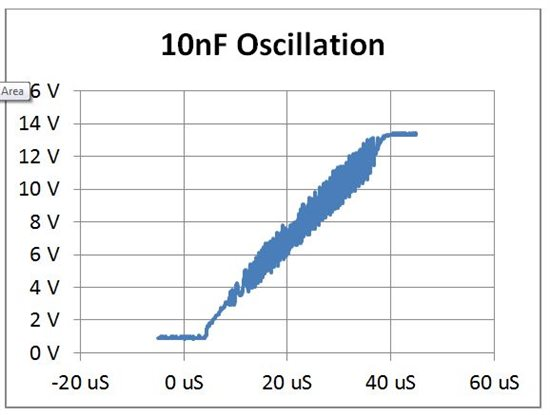

第 3 步:使用波形验证结果

当 RIN 增加到 1k ohms 或 40pF 的寄生电容被添加到驱动器输入节点时,正压摆波形上会出现 30 至 40MHz 的振荡。因此,Rin 和 Cint 应靠近驱动器输入引脚以减少走线电容,Rin 应为 402 欧姆或更小。

第 4 步:确定开关损耗

可以使用线圈电流、线圈电源电压、压摆率和频率(每秒的平均继电器周期数:通常小于 1)来估计由于延长的上升和下降时间而增加的开关损耗。因此,增加的功率损耗为 P = ½ * F * V 2 * I / Pslew。对于 V=12V,I=122mA,402 ohms + 10nF 使得 Pslew = 0.38V/uS,F = 1(开/关)周期/秒,功耗仅为 +23uW。

对于 PWM 应用(在触点保持期间降低线圈电流),每个通道增加的 PWM 功率损耗为 P = ½ * F * V 2 * I * (1/Pslew + 1/Nslew)。对于 V=12V,I = 70mA,402 ohms + 100pF 使得 Pslew = 26V/uS,Nslew = 33V/uS,F = 25kHz,每通道功率为 +17mW。

所以…… 继电器驱动器的 EMI 可以通过添加一些无源元件和小幅增加驱动器的功耗来降低。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。